Flip Flop회로(latch 회로, RS, D Flip Flop)

디지털 제어 - Flip Flop회로(latch 회로, RS, D Flip Flop)

NOR/NAND latch 회로 복습

학습목표

7402를 활용하여 NOR회로를 만들 수 있다.

7400을 활용하여 NAND회로를 만들 수 있다.

NAND회로를 활용하여 RS Flip Flop 회로를 만들 수 있다.

7474회로로 D Flip Flop 회로를 만들 수 있다.

지난 시간에 만들었던 NOR/NAND latch회로를 만들어보자!

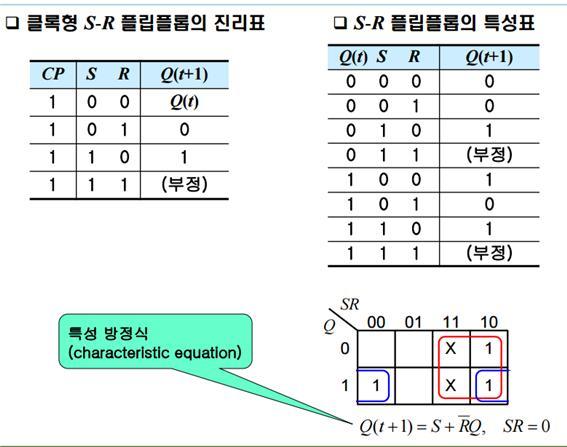

latch와 S-R 플립플롭의 가장 큰 차이는 클럭 공급의 차이이다.

클럭 공급으로 인해 데이터의 입출력이 연속이 아니라 클럭 공급의 형태로 바뀐다.

값이 1(S) 1(R)일 때 부정 값을 보완해주기 위해 나온 것이 D플립플롭이다.

/* 카르노 맵 그리는 법!

비트 2개가 한꺼번에 바뀌는 것을 방지하기 위해 SR값은 00 01 11 10으로 나열해 준다.

Q에는 2비트 값(0,1)을 기입해준다.

실습 - 클록형 S-R 플립플롭(NAND형) 만들기

클럭의 high부분에서만 데이터가 처리되는 것을 레벨(level)트리거 라고 한다. 이 때 high부분에서 전압이 일정하지 않고 잡음이 발생하여 오동작이 발생할 수 있다. 때문에 high에서 low 혹 low에서 high로 바뀌는 부분에서 동작할 수 있도록 만든 것이 에지(edge) 트리거라고 한다.

//프로테우스에서 시뮬레이션 해보면 지연이 표시되지 않기 때문에 펄스 전이 검출기 회로에서의 지연 값을 볼 수 없다.

//파란색 구간은 부정을 표시한다.

//Q(t+1) 입력의 Q와 출력의 Q를 표시해주기 위한 표시.